Table Of Content

- RTL design

- Technology

- Join the world’s largest professional organization devoted to engineering and applied sciences and get access to

- Frequently Asked Questions

- Adding your response to an article requires an IEEE Spectrum account

- Cadence Design Launches Two New Platforms For Massive Chip Designs

- Intel 2Q24 guidance disappoints, Gaudi 3 sales expected to reach US$500 million in 2024

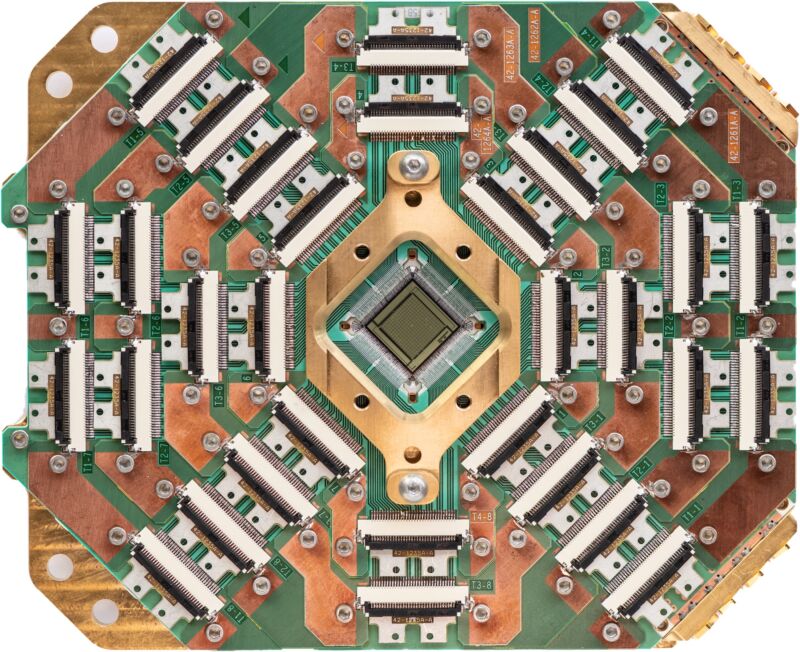

This flow spans photonic IC design with Synopsys OptoCompiler™ and integration with electrical ICs utilizing Synopsys 3DIC Compiler and Ansys multiphysics analysis technologies. "Together, TSMC and Synopsys will help engineering teams create the next generation of differentiated designs on TSMC's most advanced process nodes with faster time to results." ASIC (application-specific integrated circuit) is an integrated circuit specially constructed for a specific application or purpose.

RTL design

These devotees post glossy videos of themselves shucking chips like oysters to see their iridescent insides and the itsy bitsy sketches that may be hidden on them. Pixpa is an easy, all-in-one portfolio website builder for photographers & creators to create portfolio websites with a built-in online store, blog, and client galleries. Pro plan is available for US$9,991 per month with 1 GB storage and Free Previews.

Technology

Ericsson and Nokia branch into chip design to ride 5G and AI waves - Nikkei Asia

Ericsson and Nokia branch into chip design to ride 5G and AI waves.

Posted: Tue, 12 Mar 2024 07:00:00 GMT [source]

This chip, called simply MPW-5, was based on a new open-source tool called openFASOC, short for Open-Source Fully Autonomous System-on-Chip. OpenFASOC, developed by Saligane and a team of researchers, including Sylvester, is the open-source corollary to FaSOC, a project led by Prof. David Wentzloff, with collaborators at the University of Virginia and ARM. Another segment of AI that the semiconductor industry is starting to explore for chip development is generative AI. Based on large language models, generative AI learns the patterns and structure of input data and quickly generates content—text, videos, images, and audio, for example. Generative AI models have demonstrated their abilities in a variety of application areas, with the ChatGPT chatbot currently being one of the most publicly prominent examples.

Join the world’s largest professional organization devoted to engineering and applied sciences and get access to

This bug will have to be fixed in the next version of RTL release from the design team. This process goes on until there is a good level of confidence in the functional correctness of the design. RISC-V chips have already begun to pop up in earbuds, hard drives, and AI processors, with 10 billion cores already shipped. Companies are also working on RISC-V designs for data centers and spacecraft. In a few years, RISC-V proponents predict, the chips will be everywhere.

"At one point, I would say in '99 it was that the word was out in Tallahassee that we were collecting (chips)," said Eric Clark, who helped Davidson build the site. While drawing any shape, lines, or curves using vectors, you would not face any loss in quality when you scale it up. You can create custom design elements and use them in any of your designs.

Frequently Asked Questions

The Perspectives on Innovation Blog is produced by the Renewing American Innovation Project at the Center for Strategic and International Studies (CSIS), a private, tax-exempt institution focusing on international public policy issues. Accordingly, all views, positions, and conclusions expressed in this publication should be understood to be solely those of the author(s). Roughly saying, digital IC design can be divided into three parts.

Adding your response to an article requires an IEEE Spectrum account

So again we have to see how that goes, but that requires these really advanced LLM capabilities. But if that works well, that could be another kind of very interesting kind of application of Gen AI. Now, if we have booked that business, the deliveries will happen towards second half of the year, as John was saying earlier.

And we are involved with all the major players there, and we are glad to provide our solutions. I think, one of the biggest challenges with something like that is you know, we do small tuck-in M&A, but I don't want to go over Lee Simpson – answer Anirudh gave to Lee Simpson, but organic is delicious here. At Cadence, we focus on innovation and growing with organically driven products and then with small tuck-in M&A. But to the extent that we do some larger M&A and of course, we have BETA CAE, which apparently is the gold standard in structural simulation.

Here we present a deep reinforcement learning approach to chip floorplanning. In under six hours, our method automatically generates chip floorplans that are superior or comparable to those produced by humans in all key metrics, including power consumption, performance and chip area. To achieve this, we pose chip floorplanning as a reinforcement learning problem, and develop an edge-based graph convolutional neural network architecture capable of learning rich and transferable representations of the chip.

Kenton Smith designs circuit boards and has long been fascinated by computers. PixTeller is an easy to use editor tool that can be used to create graphic images (downloadable in PNG, JPG, PDF format) and animations (downloadable in MP4, GIF format). Anyone can use it to make images, animated gifs & videos for personal or business use, with no technical or design knowledge. Creating graphics is a time demanding process, but with this design tool, anyone can make personalized visuals from scratch or by customizing any pre-made templates in minutes. There are many customization programs and 3rd party plugins that can be used in GIMP to improve your productivity and create better designs.

The future of chip design is bright, and next-gen chipsets will enable more innovative solutions across many industries. As technology evolves, we can expect even more exciting developments in chip design and the solutions they enable. Note that the second step, RTL design, is responsible for the chip doing the right thing. The third step, physical design, does not affect the functionality at all (if done correctly) but determines how fast the chip operates and how much it costs.

No comments:

Post a Comment